本文的关键要点

・在非放电型RCD缓冲电路中,RSNB消耗的功率仅为浪涌能量,因此RSNB的容许损耗可以比较小。

・因此,可以增加CSNB的电容量,这不仅可改善钳位效果,还可提高开关频率fSW。

・通常而言,在增加了非放电型RCD缓冲电路的电路中,低负载时的效率会降低,高负载时的效率会提高。这是因为在高负载时,缓冲电路具有抑制浪涌的效果,最终会降低开关损耗。

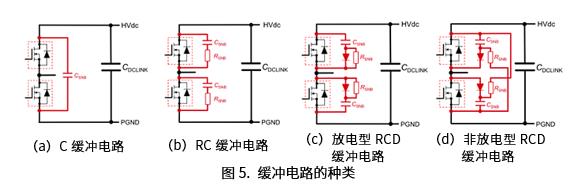

本文将介绍四种缓冲电路中的最后一种“非放电型RCD缓冲电路”的设计。

- 漏极和源极之间产生的浪涌

- 缓冲电路的种类和选择

- C缓冲电路的设计

- RC缓冲电路的设计

- 放电型RCD缓冲电路的设计

- 非放电型RCD缓冲电路的设计

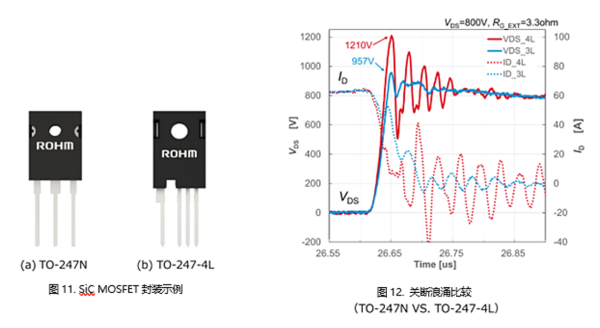

- 封装引起的浪涌差异

SiC MOSFET:非放电型RCD缓冲电路的设计

与放电型RCD缓冲电路不同,非放电型RCD缓冲电路的RSNB消耗的功率仅为浪涌能量,因此RSNB的容许损耗可以较小。这可以扩大RSNB的选择范围,使得能够增加CSNB的电容量,因而可以提高钳位的效果。

CSNB由“C缓冲电路的设计”中的公式(2)决定,RSNB由“RC缓冲电路的设计”中的公式(3)决定。但是,RSNB的功耗由下面给出的公式(6)决定。由于“RC缓冲电路的设计”的公式(4)中不存在包含CSNB和fSW的二项式,所以基本上不会有因CSNB和fSW导致的功耗增加情况。因此,可以将CSNB的电容值设置得大一些,从而可以实现钳位效果更好的缓冲电路;另外,还支持提高fSW的频率。

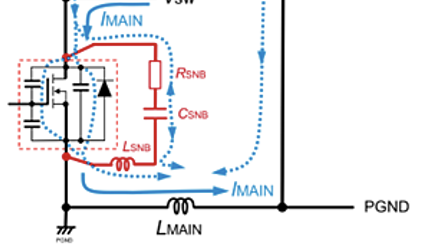

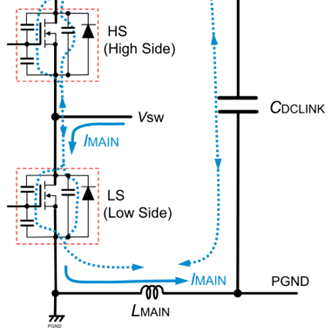

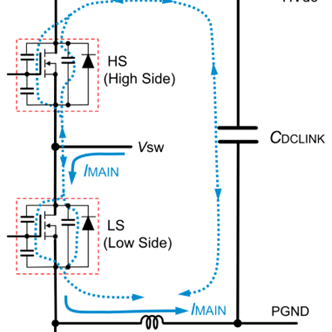

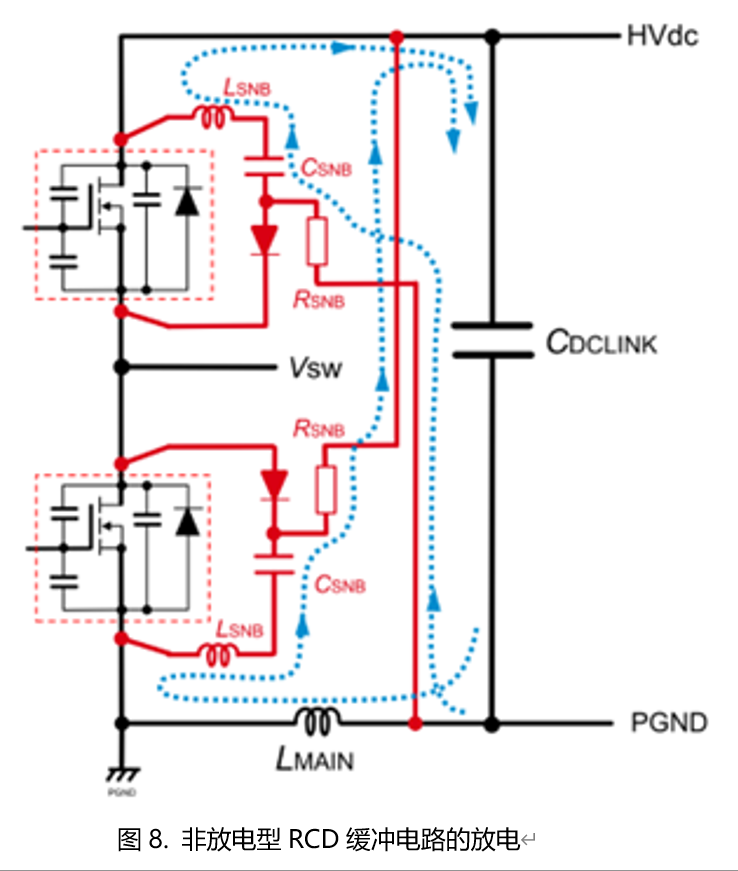

图8是非放电型RCD缓冲电路工作后的放电路径。上桥臂的浪涌电流流向PGND,下桥臂的放电电流经由RSNB流向HVdc,因此受布线电感的影响较小。另一方面,由于电流变化很大,因此在MOSFET漏极和源极之间的布线电感LSNB需要尽可能小。

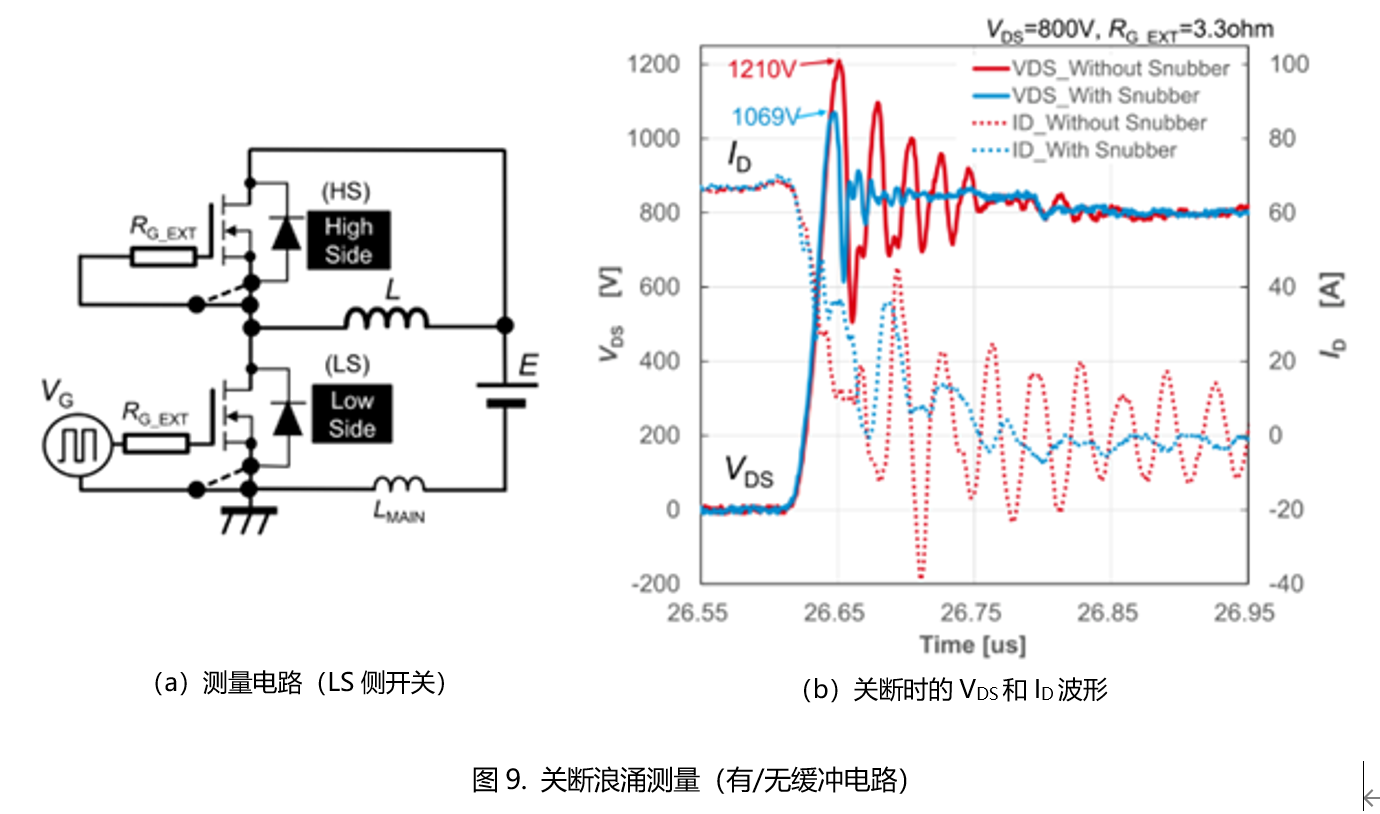

图9是通过评估板P02SCT3040KR-EVK-001验证使用了SiC MOSFETSCT3080KR的非放电型RCD缓冲电路效果的波形。(a)是测试电路,(b)是有和没有缓冲电路时的测试波形。该波形是RG_EXT=3.3Ω、HVdc=800V、漏极电流ID约为70A时的关断波形。

当不连接缓冲电路时,关断时会产生1210V的浪涌;当增加了缓冲电路后,浪涌变为1069V,降低了约12%。另外,缓冲电路还消除了伴随浪涌产生的电压振铃,因此可以大大降低EMI。

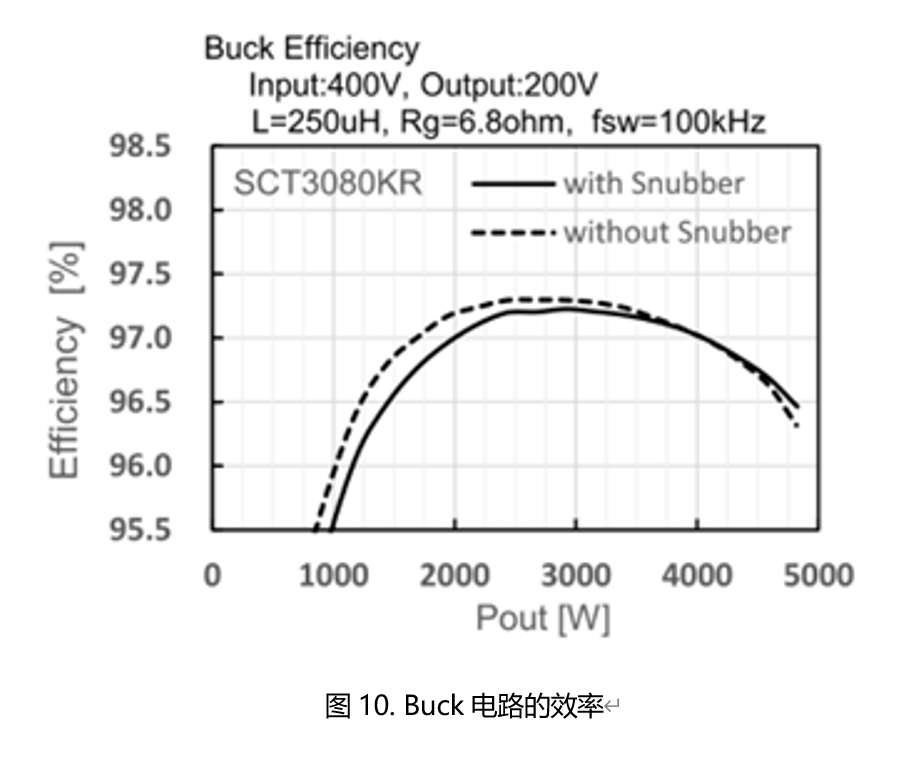

图10是在降压型转换器(Buck Converter)中的转换效率比较图。这是输入电压=400V、输出电压=200V、RG_EXT=6.8Ω、开关频率fSW=100kHz时的效率。

当使负载功率从1kW变化至4.8kW时,在约4kW以下,没有缓冲电路时的效率比有缓冲电路时最大高0.4%;在4kW以上,有缓冲电路时的效率比没有缓冲电路时高0.15%。这是因为,随着负载功率的增大,浪涌引起的功率损耗(谐振电流引起的电容器等的等效串联电阻的损耗)也会增加,利用缓冲电路来抑制浪涌,最终会使开关损耗降低。