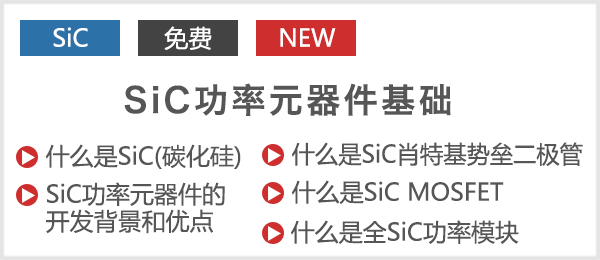

本文的关键要点

・SiC MOSFET的封装类型不同,在漏极和源极之间产生的浪涌也不同。

・与TO-247N相比,TO-247-4L通过改变驱动电路的路线加快了开关速度,因此浪涌通常更大。

本文将介绍“SiC MOSFET的封装不同,在漏极和源极之间产生的关断浪涌也不同”相关的内容,这也是在设计之前需要掌握的知识。

SiC MOSFET:封装引起的浪涌差异

下面通过一个案例来介绍因SiC MOSFET的封装不同而导致的浪涌差异。

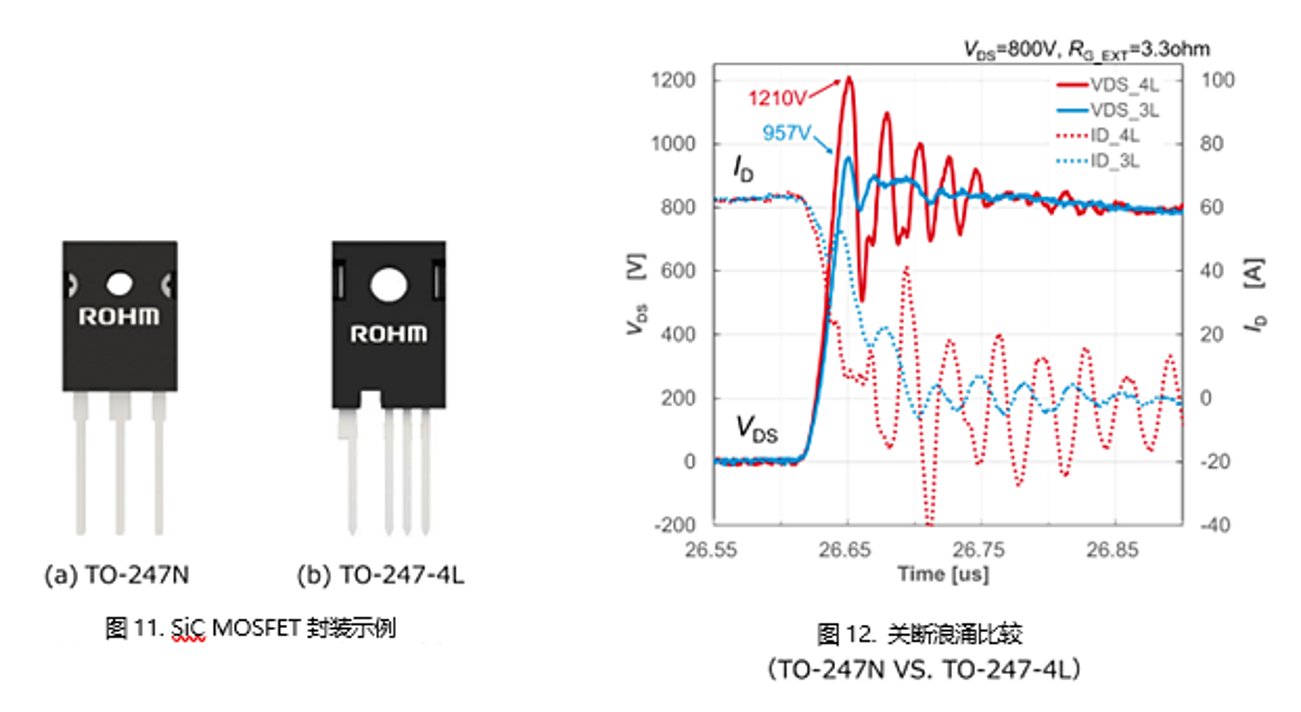

图11是SiC MOSFET的典型封装。(a)是被广泛使用的TO-247N封装(3个引脚);(b)是近年来应用逐渐增加、配有驱动电路用源极引脚(所谓的“开尔文连接”)的TO-247-4L封装(4个引脚)。

与(a)TO-247N相比,(b)TO-247-4L是通过改变驱动电路的路径加快了开关速度的封装。因此,其导通时的浪涌和关断浪涌往往比(a)中的更大。

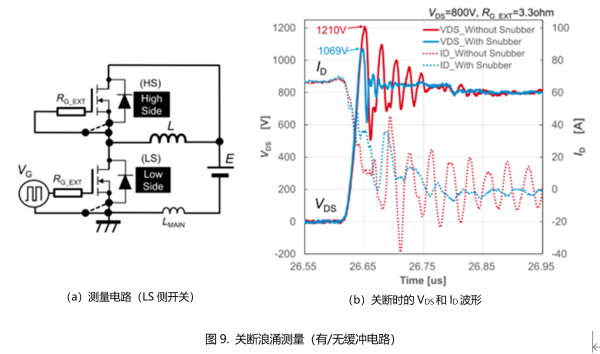

图12是这两种封装产品的关断浪涌比较波形。测试电路与“非放电型RCD缓冲电路的设计”中图9(a)的电路相同。这是VDS=800V、RG_EXT=3.3Ω、ID=65A时的关断波形。(a)TO-247N(3L,蓝线)的漏极-源极间浪涌为957V,而(b)TO-247-4L(4L,红线)的则高达1210V。

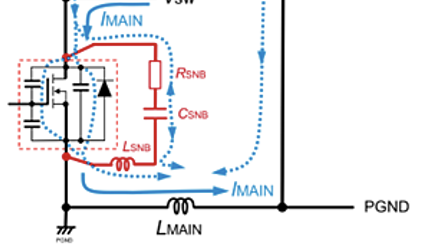

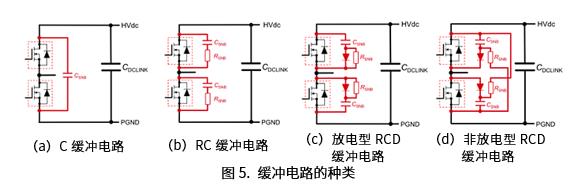

如“非放电型RCD缓冲电路的设计”的图7和图8所示,由该浪涌引起的VDS振铃不仅会流过CDS,还会流过CDG和CGS,这可能会导致MOSFET的栅-源电压VGS产生意外浪涌,有时可能会超过VGS的浪涌限值。对此,我们已经在Tech Web基础知识的“SiC MOSFET:栅极-源极电压的浪涌抑制方法”和另外的应用指南(*2)中详细介绍了VGS浪涌的抑制方法,如果仅凭这些措施浪涌抑制效果还不够,那么可以考虑通过在漏极和源极之间增加缓冲电路来抑制浪涌。

*2:“栅极-源极电压的浪涌抑制方法”应用指南(No. 62AN009J Rev.002)ROHM Co., Ltd.,2020年4月