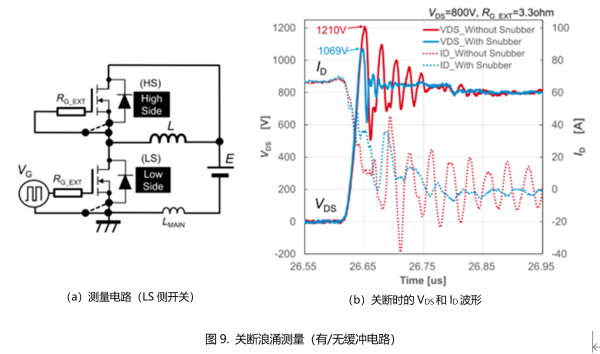

与传统的功率半导体相比,SiC MOSFET的开关速度更快,因此其电压和电流变化更急剧。这使得器件自身的封装电感和外围电路的布线电感等的影响变大(已经不容忽视),最终会导致较大的浪涌。关于这种浪涌的抑制方法,我们已经介绍过其中一种,即缓冲电路的增加方法和设计方法。

以下是迄今为止发布的相关文章链接和关键要点汇总。

本文的关键要点

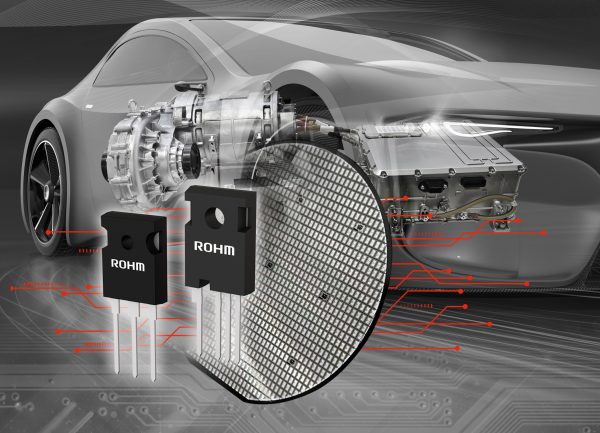

・近年来,SiC MOSFET因其能够高速开关工作而被广泛用于各种功率转换应用。

・但是,高速工作会在漏极和源极之间产生较大浪涌,需要采取措施抑制这种浪涌。

・缓冲电路是抑制浪涌的方法之一。

本文的关键要点

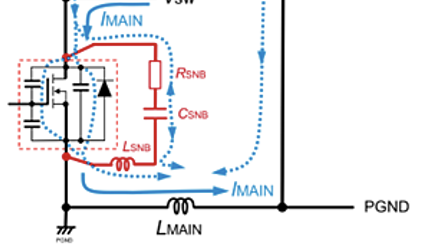

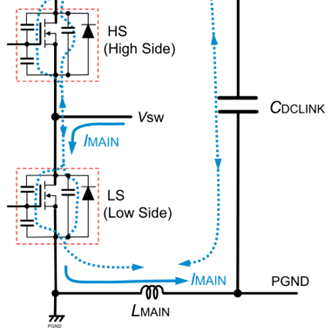

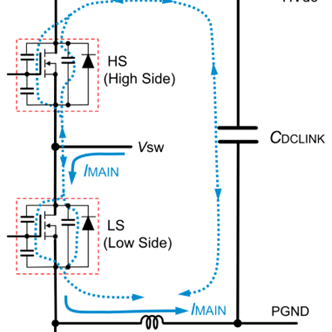

・漏极和源极间的浪涌是由各种电感分量和MOSFET寄生电容的谐振引起的。

・在实际的设计中,很多情况下无法设计出可将布线电感降至最低的布局,此时,在尽可能在靠近开关器件的位置配置缓冲电路来降低布线电感是非常重要的。

本文的关键要点

・要想使缓冲电路充分发挥出其效果,需要尽可能靠近开关器件进行安装。

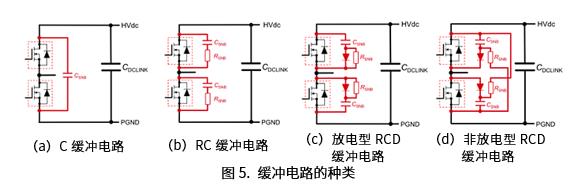

・缓冲电路包括由R、L、C等无源元件组成的电路和由半导体元器件组成的有源电路。

・本文介绍了无需控制而且具有成本优势的电路方式——C缓冲电路、RC缓冲电路、放电型RCD缓冲电路和非放电型RCD缓冲电路。

本文的关键要点

・CSNB越大,C缓冲电路的浪涌抑制效果越好。

・但是,需要注意的是,缓冲电路中形成的LSNB需要低于LMAIN,关于LSNB,还需要考虑电容器的ESL。

本文的关键要点

・RC缓冲电路需要考虑到功耗PSNB来求出CSNB和RSNB,并将其谐振角频率ωSNB设置得充分高于浪涌的谐振角频率ωSURGE。

本文的关键要点

・放电型RCD缓冲电路的设计与RC缓冲电路的设计基本相同。

・但是,由于浪涌被二极管吸收,因此无需使用“RC缓冲电路的设计”一文中所示的公式(5)来确认谐振频率。

・需要选择反向恢复电流小的二极管。

本文的关键要点

・在非放电型RCD缓冲电路中,RSNB消耗的功率仅为浪涌能量,因此RSNB的容许损耗可以比较小。

・因此,可以增加CSNB的电容量,这不仅可改善钳位效果,还可提高开关频率fSW。

・通常而言,在增加了非放电型RCD缓冲电路的电路中,低负载时的效率会降低,高负载时的效率会提高。这是因为在高负载时,缓冲电路具有抑制浪涌的效果,最终会降低开关损耗。

本文的关键要点

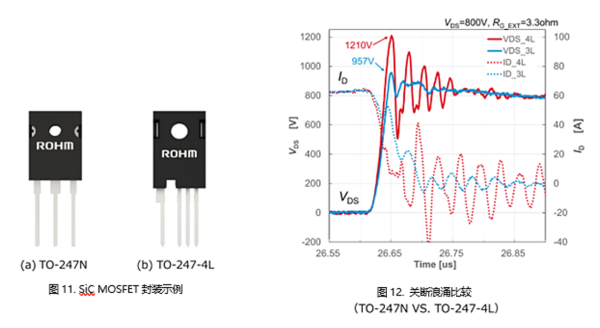

・SiC MOSFET的封装类型不同,在漏极和源极之间产生的浪涌也不同。

・与TO-247N相比,TO-247-4L通过改变驱动电路的路线加快了开关速度,因此浪涌通常更大。

【资料下载】SiC功率元器件基础

推荐阅读 同一主题文章一览

- SiC MOSFET:缓冲电路的设计方法 —前言—

- 漏极和源极之间产生的浪涌

- 缓冲电路的种类和选择

- C缓冲电路的设计

- RC缓冲电路的设计

- 放电型RCD缓冲电路的设计

- 非放电型RCD缓冲电路的设计

- 封装引起的浪涌差异

- SiC MOSFET:缓冲电路设计方法 —总结—【阅读中】