在降压型DC-DC转换器中使用第4代SiC MOSFET的效果

本文的关键要点

・介绍在降压型DC-DC转换器中的高边SiC MOSFET和低边SiC MOSFET所产生的各种损耗。

・SiC MOSFET的总损耗是各种损耗的总和。

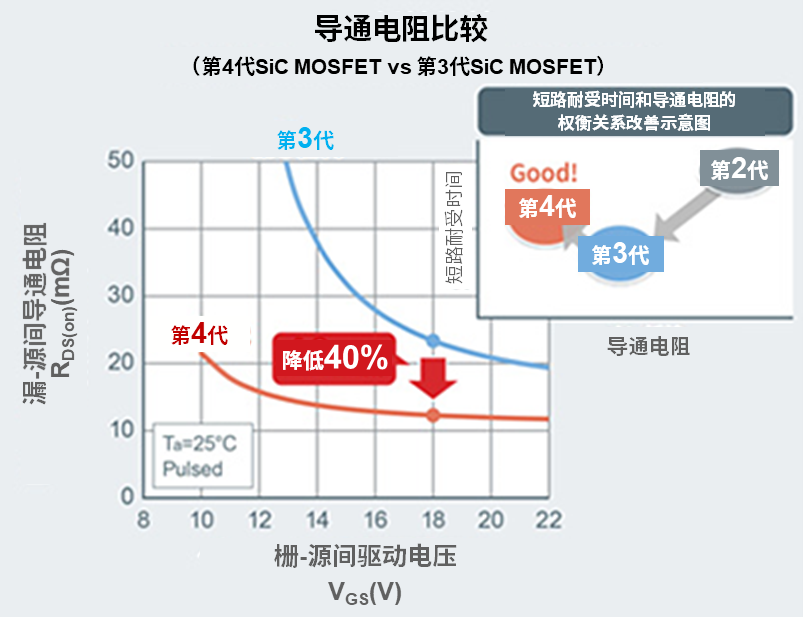

・通过将Qgd降低至第3代SiC MOSFET的一半左右,第4代SiC MOSFET可实现更低的开关损耗。

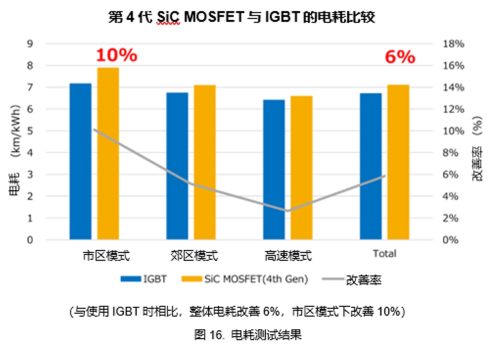

・降低开关损耗可以为客户带来诸多好处,例如进一步提高DC-DC转换器的开关频率;在负载变化率大且整体上多以轻负载模式运行的EV中,可降低损耗,从而延长续航里程,降低运行成本。

在介绍“在降压型DC-DC转换器中使用第4代SiC MOSFET的效果”之前,我们先来了解一下电路工作原理和损耗分析。

- 第4代SiC MOSFET的特点

- 在降压型DC-DC转换器中使用第4代SiC MOSFET的效果

> 电路工作原理和损耗分析

> DC-DC转换器实机验证 - 在EV应用中使用第4代SiC MOSFET的效果

> EV应用

> 装入牵引逆变器实施模拟行驶试验

> 图腾柱PFC实机评估

在降压型DC-DC转换器中使用第4代SiC MOSFET的效果:电路工作原理和损耗分析

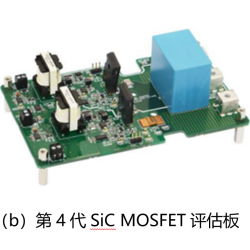

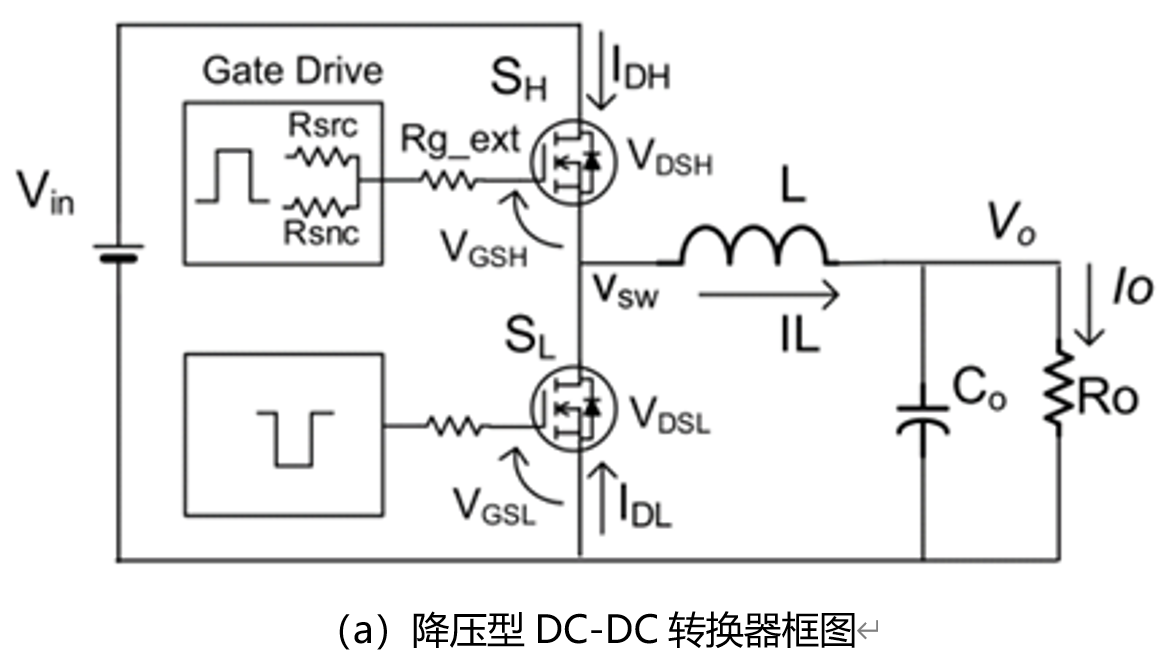

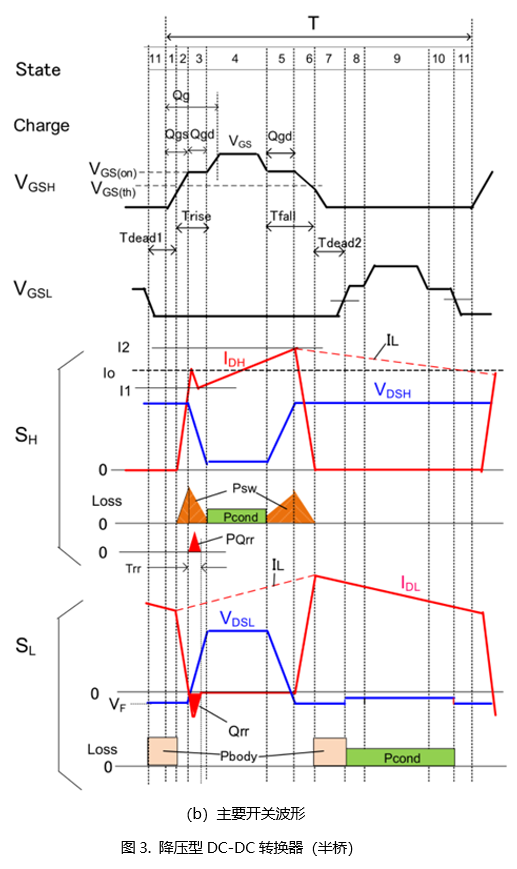

与第3代SiC MOSFET相比,第4代SiC MOSFET的高速开关特性改善尤为明显,这将非常有助于降低开关损耗。图3(a)是降压型DC-DC转换器的框图,图3(b)是其开关波形。

如图3(b)所示,DC-DC转换器中的功率器件SH和SL的损耗包括开关损耗Psw、传导损耗Pcond、体二极管损耗Pbody、反向恢复损耗PQrr和Coss损耗。(*由于Coss损耗很小,因此图中省略了Coss损耗)

在技术规格书中,开关损耗通常表示为Eon、Eoff的每个脉冲所消耗的能量。这个指标在初期设计阶段进行损耗粗略估算时很有用。在具体设计中,需要严谨地计算出在高电压输入和高频条件下的损耗。栅极电压值、栅极驱动器的Sink/Source电阻值、外置栅极电阻值等几Ω的值,会在几ns(纳秒)量级影响到开关时间(Trise/Tfall)。而这最终会导致损耗显著变化,因此栅极驱动器的优化设计将需要用到SiC MOSFET的高速开关特性。

高边SiC MOSFET SH产生的损耗

开关损耗仅由高边SiC MOSFET SH产生,通过公式(1)表示。下面来讲解其机理。

在State 1【图3(b)中的T期间编号,下同】,栅极电压VGS施加在高边SiC MOSFET(SH)上,当在State 2超过阈值VGS(th)时,电感电流开始快速流过SH时,电感电流开始快速流过VGS(on)(平台电压)之前的短短几纳秒内即可达到负载电流Io。然后在State 3(电压平台期)期间通道开通, VDS达到0V。State 2 和State 3期间是公式(2)中所示的导通时的开关期间Trise。在技术规格书中通常不会给出State 2的电荷量,所以在公式(2)中电荷量是通过Qgs估算的,用系数k进行调整(通常k为1/3-1/4)。

另外,栅极电流Ig_on是由栅极驱动器电压VGS和栅极导通电压VGS(on)之间的电位差以及那里存在的电阻量决定的,因此可通过公式(3)来计算。公式中的Rsrc表示栅极驱动器的源极电阻,Rg_ext表示外置栅极电阻,Rg_int表示SiC MOSFET内部栅极电阻。

(后面再讲State 4)

栅极电压下降,进入关断状态(State 5-6)。该Tfall期间由公式(4) 表示。需要注意的是,如公式(5)所示,Tfall期间的栅极电流Ig_off的分子只有VGS(on)。一般情况下,关断时间会稍长。公式中的Rsnk表示Sink电阻。

在可以将其视为电感负载类的恒流源的情况下,由于电流波形波ID和电压波形VDS变化的时序不会重叠,因此公式(1)中开关损耗Psw的系数为1/2。

另外,在该Trise期间,由于存储在漏-源电容CossH中的电荷会在通道中短路,因此会产生公式(6)所示的充放电损耗PcossH。

在State 4中,在高边SiC MOSFET SH完全导通期间产生传导损耗PcossH[公式(7)]。此时的有效电流使用占空比D(=Vo/Vin)通过公式(8)求出。

以上就是高边SiC MOSFET SH产生的开关损耗、传导损耗及Coss损耗。

低边SiC MOSFET SL产生的损耗

接下来,我们来了解一下低边SiC MOSFET SL产生的损耗。

State 7、State 11及State 1是死区时间。流向低边SiC MOSFET SL的体二极管的传导电流会产生损耗[公式(9)]。

在State 8~10中,低边SiC MOSFET SLの会产生传导损耗[公式(10)]。此时的有效电流通过公式(11)求得。

低边SiC MOSFET SL的Coss充放电损耗在 SL导通时(State 8)通常会被忽略,这是因为Coss电荷已经通过电感电流IL被放电而成为ZVS(Zero Voltage Switching)。

以上就是低边SiC MOSFET SL产生的损耗。

反向恢复损耗PQrr

反向恢复损耗PQrr发生的时间点是在State 3,是由低边SiC MOSFET SL的体二极管的反向恢复特性引起的损耗[公式(12)]。该损耗由高边SiC MOSFET SH和低边SiC MOSFET SL共同导致,在这里为了简单起见,归在高边SiC MOSFET SH产生的损耗中。

总损耗

综上所述,高边SiC MOSFET SH和低边SiC MOSFET SL的总损耗分别通过公式(13)和公式(14)求得。

尤其是关于开关损耗Psw,由公式(2)和公式(4)可知,Qgd(对栅-漏电容充电的米勒平台电荷量)越小,Trise/Tfall的时间越短,因此公式(1)中的开关损耗Psw得以降低。通过将Qgd降低至第3代SiC MOSFET的一半左右,第4代SiC MOSFET可实现更低的开关损耗。

这将有助于提高DC-DC转换器的开关频率,另外,在负载变化率大且整体上多以轻负载模式运行的EV中,可有效降低损耗,从而延长续航里程,降低运行成本。使用第4代SiC MOSFET所带来的这些效果,将会给客户来带很大的优势。

【资料下载】了解碳化硅功率元器件及其应用案例

介绍了在电源产品的小型化、降低功耗和提高效率方面具有巨大潜力的碳化硅(SiC)的基本物理特性,以及SiC二极管和晶体管的使用方法及其应用案例。

“电路工作原理和损耗分析”相关的文章一览

- 使用新一代SiC MOSFET降低损耗实证 —前言—

- 在EV应用中使用第4代SiC MOSFET的效果:图腾柱PFC实机评估

- 使用新一代SiC MOSFET降低损耗实证 —总结—

- 第4代SiC MOSFET的特点

- 在降压型DC-DC转换器中使用第4代SiC MOSFET的效果

- DC-DC转换器实机验证

- 在EV应用中使用第4代SiC MOSFET的效果

- 在EV应用中使用第4代SiC MOSFET的效果:EV应用

- 在EV应用中使用第4代SiC MOSFET的效果:装入牵引逆变器实施模拟行驶试验