上一篇文章对全SiC模块栅极驱动的评估事项之一“栅极误导通”进行了介绍。本文将作为“其2”介绍栅极误导通的处理方法。

“栅极误导通”的抑制方法

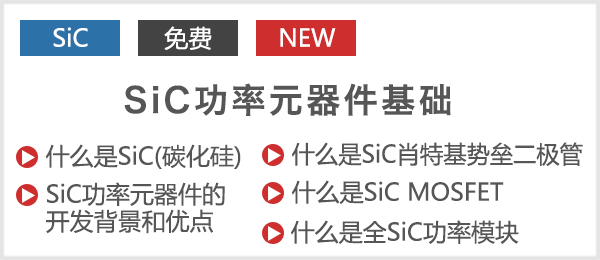

栅极误导通的对策方法有三种。

①是通过将Vgs降至负电压(而非0V),使Vgs即使上升也不会达到阈值的增加余量方法。这种方法需要负的栅极驱动电压,所以栅极驱动器的电源要使用+18V/-3V这样的不对称的两个电源。在这种情况下,需要将负电压设置为不超过Vgs的最大额定值。

②是在栅极-源极间增加外置电容器,降低阻抗,抑制栅极电位升高的方法。这里需要注意的是CGS也会造成损耗,因而需要适当的电容。

③是在栅极-源极间增加米勒钳位用MOSFET的方法。通过在SiC-MOSFET关断时导通该MOSFET,强制使Vgs接近0V,从而避免栅极电位升高。

评估电路中的确认

使用评估电路来确认栅极电压升高的抑制效果。下面是栅极驱动电路示例,栅极驱动L为负电压驱动。CN1和CN4的+18V、CN3和CN6的-3V为驱动器的电源。电路中增加了CGS和米勒钳位MOSFET,使包括栅极电阻在内均可调整。将该栅极驱动器与全SiC功率模块的栅极和源极连接,来确认栅极电压的升高情况。

下面确认增加了②的外置CGS时的效果。首先来看没有外置CGS时的数据。如前一篇文章所述,低边的栅极电阻Rg越小Vgs越高。

接下来请看增加了2.2nF外置CGS后的数据。如2.2nF的曲线所示,栅极电压的上升程度得到了抑制。

再看将CGS增加到5.6nF时的数据。虽然电容增加,但抑制效果却不明显。

从图中可以看出,结论是增加CGS可以有效抑制Vgs的上升程度,但并非单纯地提高电容器的电容其抑制效果就更好。如前所述,CGS也是造成损耗的因素,所以电容器需要选择适当的电容值。

接下来请看③的米勒钳位MOSFET的效果。圆点是添加上述CGS的数据,中空圆点是米勒钳位数据。可见效果非常好。右图表示关于浪涌电压,任何条件下都几乎相同。

最后是实际的波形。绿色和蓝色是对策前的波形,红色和橙色是对策后的波形。条件如表所示,对策后增加了米勒钳位MOSFET,Rg从3.9Ω降至2.2Ω,并增加了5.6nF的CGS。

Id和Vd在对策后振铃均变小。关于Vgs,在Vgs(L)时观察到峰值升高5.9V,对策后被抑制到1.1V。在Vgs(H)时峰值为7.7V的振铃在对策后降至3.5V,可见收敛速度很快。

综上所述,通过优化全SiC功率模块的栅极驱动,可实现更低损耗的清洁运行。