目录

开关噪声是由电流突然通断(ON/OFF)切换引发的高频振铃,尤其常见于开关电源及高速工作的半导体器件中。这类噪声虽可通过优化电路板布线实现降噪,但针对泄漏的辐射噪声,需采取专门的应对措施。此外,平行布线之间会产生串扰,进而引发感应噪声。本文以DC-DC转换器为例,详细阐述开关噪声的产生原理、电子电路设计中开关噪声对电磁兼容性(EMC)等方面的影响,以及针对这些问题的有效解决方案。

什么是开关噪声?

开关噪声是电子电路及电源IC(集成电路)工作过程中,由不必要的电流波动引发的高频振铃。这类噪声常见于DC-DC转换器、AC-DC转换器等高速运行的半导体器件中。开关噪声可能降低电路稳定性,还可能引发电磁兼容性(EMC)中的电磁干扰(EMI)相关问题。

开关噪声的产生原因

开关噪声的常见原因是由开关电源等可高速通断的半导体器件工作所导致。由此会产生急剧的电流或电压变化,进而引发纹波与噪声。

噪声对策(噪声消除与降低)

针对开关噪声的降低与消除,可采取以下几项对策:

- 1. 使用滤波器:通过低通滤波器或高通滤波器,去除不必要的频率成分。

- 2. 配置电容器:在电路的关键位置配置电容器,吸收电压波动。

- 3. 电路板布局的噪声对策:尽量缩短布线长度,通过优化布局降低开关噪声(传导噪声)。

- 4. 缓冲电路:使用缓冲电路吸收振铃,从而可以降低开关噪声(辐射噪声)。

- 5. 自举电路的噪声对策:插入电阻,能够降低开关噪声(辐射噪声)。

噪声对策的重要性

通过采取有效的开关噪声对策,电路的工作会更加稳定,性能也能得到提升。尤其在高精度电子设备及工业领域的应用中,开关噪声对策更是必不可少的。

本文后续将以DC-DC转换器为例,详细讲解所产生的共模噪声和差模噪声的相关原因及对策,此外还会深入说明串扰的定义、以及缓冲电路等的辐射噪声应对方法。理解这一系列内容后,便能实施更高级别的噪声对策。

DC-DC转换器中开关噪声的产生原理

开关噪声的产生原因,是电子电路或电源IC工作过程中出现的不必要电流波动,进而引发高频振铃。下面将以DC-DC转换器为例,对开关噪声进行说明。

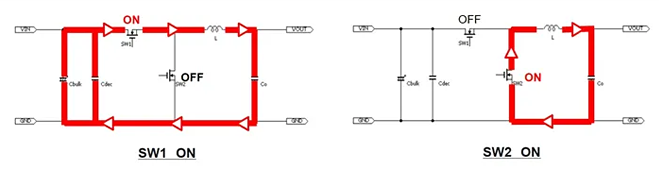

首先,我们将借助同步整流型降压DC-DC转换器的等效电路,确认开关电流的路径。

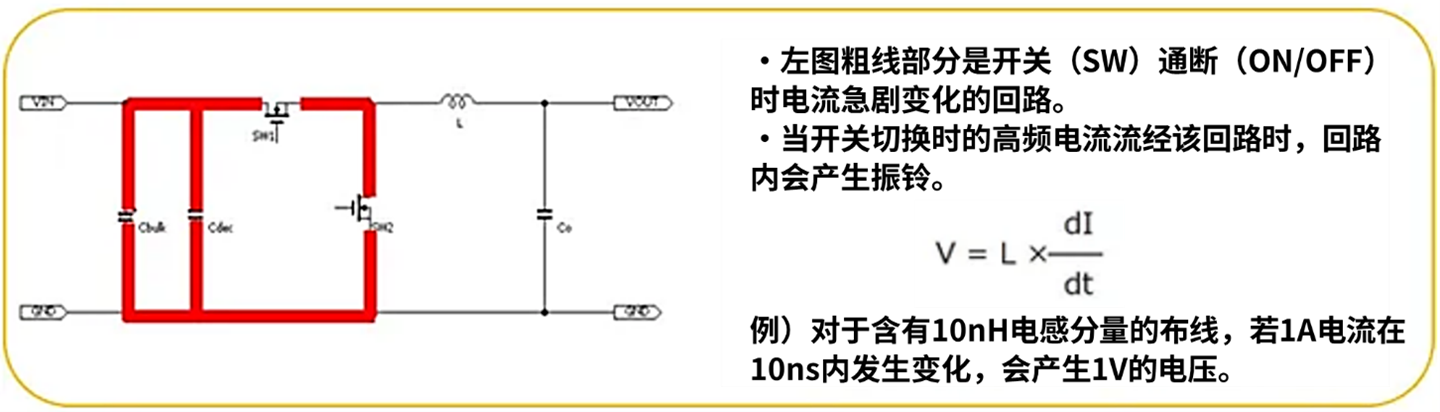

设高边开关为SW1,低边开关为SW2。当SW1导通(SW2断开)时,电流路径为:输入电容器→SW1→电感L→输出电容器。当SW2导通(SW1断开)时,电流路径为:SW2→电感L→输出电容器。下图展示了这两种电流路径的差异,每次开关导通/断开(ON/OFF)时,红色线路中的电流发生剧烈变化。由于该回路的电流变化十分陡峭,电路板布线的电感会在回路内引发高频振铃。

下图展示了电源电路的外接元器件及实装电路板的寄生分量与振铃之间的关系。

上图中,电流急剧变化的回路里,用红色标注了寄生分量。

布线存在布线电感,通常每1mm约有1nH的电感量。此外,电容器存在等效串联电感(ESL),MOSFET 的各引脚间则存在寄生电容。受这些因素影响,开关节点会产生红框图示所示100MHz至300MHz的振铃。产生的电流与电压可通过以下两个公式计算得出:

\(I = C \times \frac{dV}{dt}, \quad V = L \times \frac{dI}{dt}\)

这种振铃会以高频开关噪声的形式产生多种影响。虽然需要采取应对措施,但由于电源IC本身无法去除电路板的寄生分量,因此需通过电路板布线布局及去耦电容器来应对。关于电路板布局,在DC-DC转换器的“电路板布局”章节 会展开详细说明。

关于“差模噪声与共模噪声”“串扰”,后续将进行说明。

关于“共模滤波器”,请参阅本链接的内容。

差模噪声与共模噪声:原因及对策

开关噪声所属的电磁干扰(EMI)主要分为“传导噪声”和“辐射噪声”两大类。

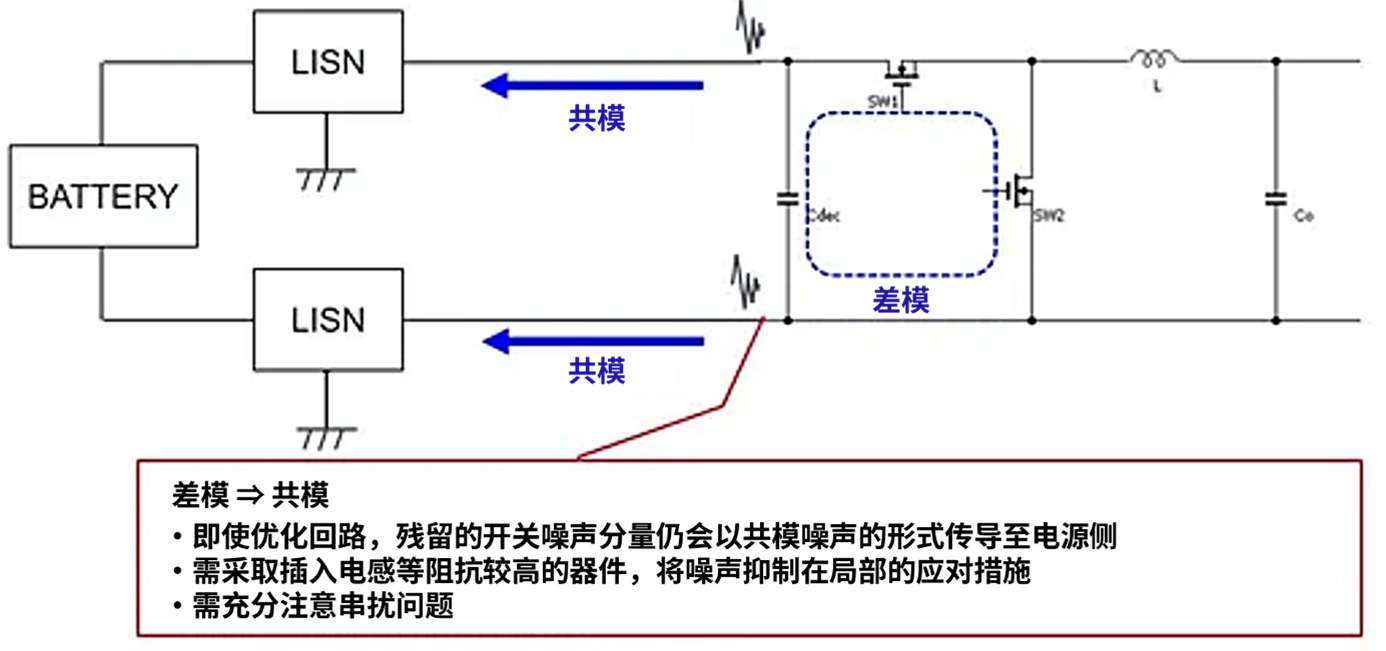

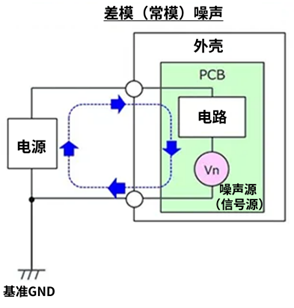

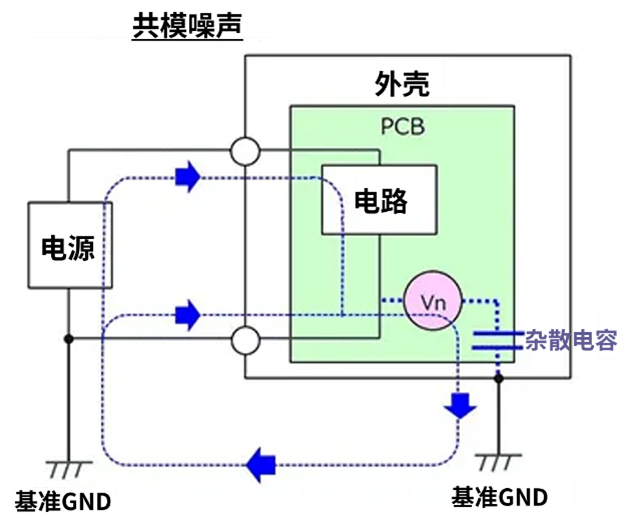

传导噪声可进一步分为两类:一类是“差模噪声”,又称“常模噪声”。这两种称呼有时可根据条件区分使用,但本文中将二者视为同一概念。另一类是“共模噪声”。下面结合图示进行说明。由于本文围绕电源相关内容展开,因此图示以“将带有电路的印刷电路板(PCB)装入外壳,并由外部供电”为例。

需特别注意的是,即使在相同条件下,共模噪声引发的辐射强度也远大幅高于差模噪声。

差模(常模)噪声与共模噪声

差模噪声是指噪声源串联于电源线路中,噪声电流与电源电流流向一致,且产生于电源线路之间的噪声。由于往返方向相反,故称为“差模(Differential mode)”。

- 噪声电流与电源电流沿同一路径流动

- 噪声电压产生于电源线路之间

共模噪声是指通过杂散电容等泄漏的噪声电流,经由大地回流至电源线路的噪声。由于电源正极(+)与负极(-)侧的噪声电流流向相同,因此被称为“共模(Common mode)”噪声。这类噪声不会在电源线路之间产生噪声电压。

- 电源线路之间不会产生噪声电压

- 电源线路与基准GND之间会产生噪声电压

- 电源正极、负极侧的噪声电流流向相同

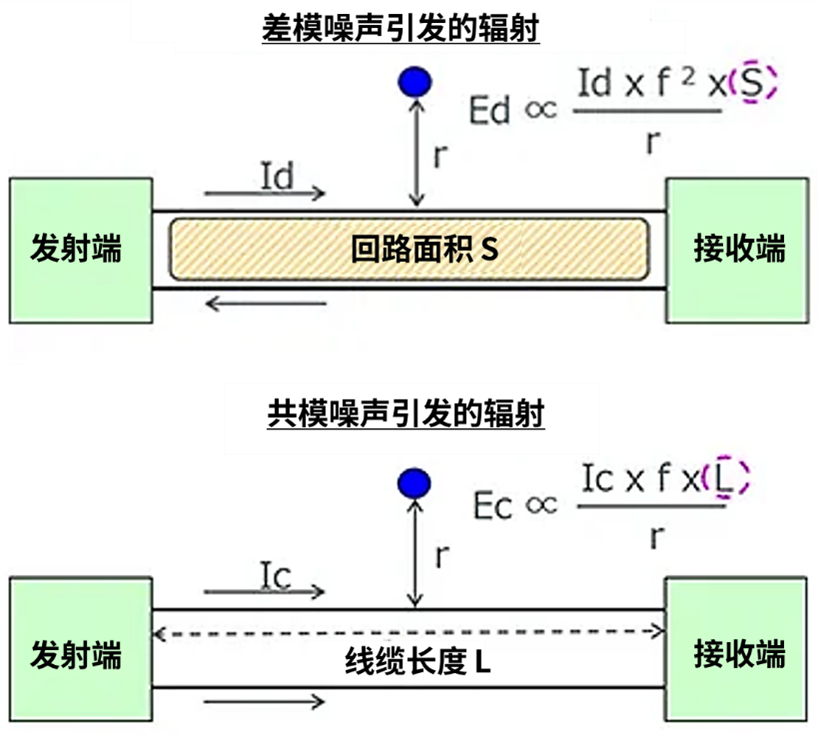

如前所述,这些开关噪声属于传导噪声。但由于噪声电流会在电源线路中流动,因此会产生噪声辐射。

由差模噪声引起的辐射的电场强度Ed可通过左下方的公式来表示。Id为差模中的噪声电流,r为到观测点的距离,f为噪声频率。差模噪声会产生噪声电流环,因此环路面积S是非常重要的因素。如图和公式所示,假设其他因素固定,环路面积越大则电场强度越高。

由共模噪声引起的辐射的电场强度Ec可通过右下方的公式来表示。如图和公式所示,线缆长度L是非常重要的因素。

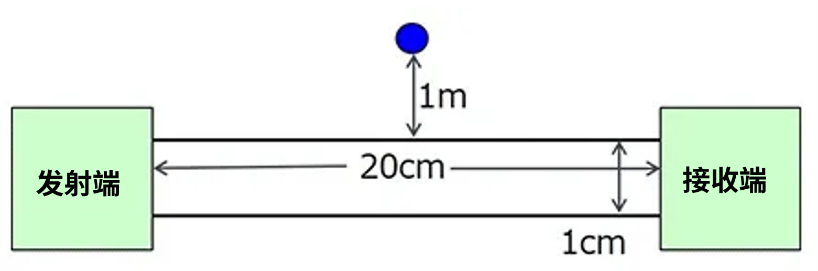

这里,为了确认各类噪声引发辐射的特征,我们尝试代入实际数值计算电场强度(*1)。所有条件保持完全一致,电场强度的观测点用蓝色圆点来表示。

*1:公式出处——《EMC工学详解 实用降噪技法》,作者:亨利・W・奥特(Henry W. Ott),东京电机大学出版社

差模噪声的电场强度计算

假设频率100MHz、1μA的差模噪声电流,在面积为20cm²的回路中流动。

则在距离1m处(90度方向)的电场强度计算如下:

\(E_d = 1.316 \times 10^{-14} \times \frac{Id \cdot f^2 \cdot S}{r}\)

\( = 1.316 \times 10^{-14} \times \frac{1\mu A \cdot (100MHz)^2 \cdot (0.2 \times 0.01)}{1}\)

\( = 0.26 \, \mu \text{V/m}\)

共模噪声的电场强度计算

假设频率100MHz、1μA的共模噪声电流,在20cm的线缆中流动。

则在距离1m处(90度方向)的电场强度计算如下:

\(E_d = 1.257 \times 10^{-6} \times \frac{IC \cdot f^2 \cdot L}{r}\)

\( = 1.257 \times 10^{-6} \times \frac{1\mu A \cdot 100MHz \cdot 0.2}{1}\)

\( = 25.1 \, \mu \text{V/m}\)

该计算结果的核心要点是:即便噪声电流值相同,共模噪声引发的辐射也远比差模噪声强烈(本示例中约为100倍)。无论如何,若这些传导噪声与辐射噪声(即电磁干扰EMI)超出允许范围,就必须采取噪声对策。尤其需要注意的是,在考虑辐射噪声对策时,针对共模噪声的防控尤为关键。

关于具体对策,后续将按顺序逐步说明。其中最基础的原则性对策如下:对于差模噪声,需减小回路面积S(例如将线缆改为绞合线),对于共模噪声,则应尽量缩短线缆长度。但实际应用中,往往会受到安装布局或材料等因素的限制,因此需考虑增设滤波器等解决方案。

本节核心目标是让读者先理解噪声的种类与基本特性。

什么是EMC?

“EMC(电磁兼容性)”是什么?关于其与“EMI(电磁干扰)”“EMS(电磁敏感性)”的含义区别及使用场景差异,下文进行了详细说明。

https://techclass.rohm.com.cn/knowledge/emc/s-emc/01-s-emc/6347

串扰(平行布线间产生的感应噪声)

串扰指的是在平行布置的布线之间,信号或噪声非预期相互传递的现象。这一问题在模拟通信及音频领域也被称为“漏话”,尤其在模拟电话中曾是极为常见的问题。此外,该现象还可称为“混线”或“串音干扰”。

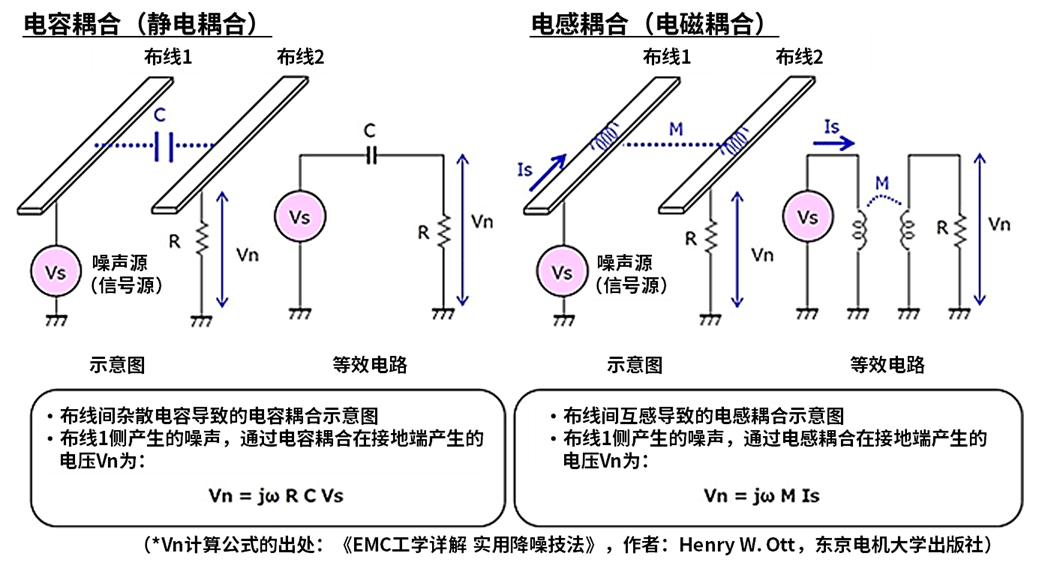

这种不必要的信号传递,是由布线间存在的杂散(寄生)电容及互感引起的。比如说,在印刷电路板(PCB)的薄膜布线等场景中尤为显著。此类场景下的信号传递通常被归为“感应噪声”。

串扰现象的根本原因有两点:一是杂散(寄生)电容导致的静电耦合,二是互感引发的电磁耦合。本文将详细讲解这些成因机制、具体应对方法,以及为帮助理解而简化的等效电路。

两种情况均给出了噪声电压Vn的公式。该电压在噪声源布线(布线1)向邻近布线(布线2)耦合时产生。R为电阻值、C为电容值、M为互感系数、Vs为噪声源电压、Is为噪声源电流。

需明确的是平行布线之间会产生串扰。此外,当布线相互垂直时,寄生电容及互感会显著减小。

电容器的抑制开关噪声对策

在对开关噪声的基本理解逐步加深后,接下来我们详细学习实际的噪声对策。其中,电容器在噪声抑制中是非常重要的元件。

在“使用电容器的开关噪声对策”中,详细介绍了电容器的阻抗特性,以及ESR、ESL等参数对噪声的影响机制。此外,还介绍了去耦电容器的有效使用方法,以及针对高频噪声抑制的特殊注意事项。

感兴趣的读者,欢迎前往“使用电容器的开关噪声对策”页面进一步了解。该页面涵盖了大量实用知识,能帮助您在开关电源的噪声对策上更进一步,为设计更高性能的电子电路提供支持。

辐射噪声(噪声电场强度)的抑制对策

什么是辐射噪声(噪声电场强度)?

在DC-DC转换器的开关噪声抑制中,辐射噪声(噪声电场强度)是另一项必须考虑的关键内容。辐射噪声由开关导通与关断波形的上升沿/下降沿斜率及振铃引起,其频率带宽约为100MHz~300MHz。

开关电源电压上升沿与下降沿的振铃,主要由MOSFET与输入电容器之间的布线电感导致。通过优化输入电容器的布局涉及与布线方式,可有效降低此类噪声。

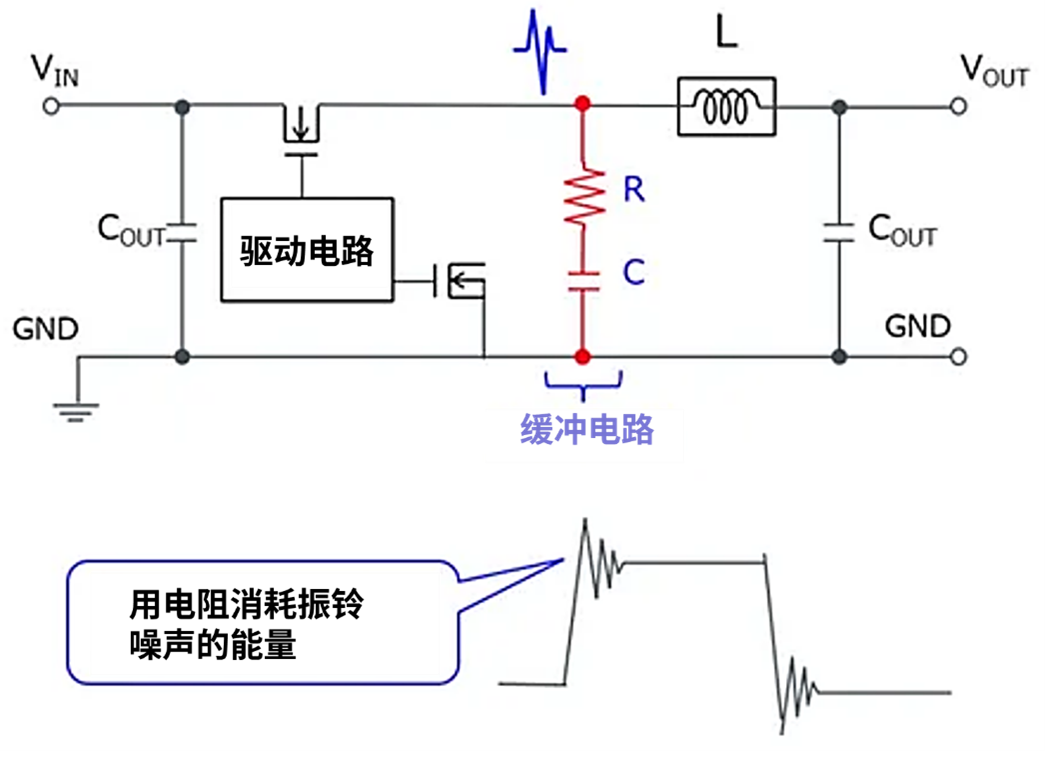

通过增设缓冲电路的开关噪声对策

当DC-DC转换器电路的辐射噪声超出设备必须满足的合规标准时,可采取平缓开关波形和增设缓冲电路的方法。

增设缓冲电路是降低开关噪声中广泛应用的方法。针对开关节点的噪声降低,需在输出端配置缓冲电路;而针对输入端噪声,则需在输入端增设缓冲电路。本示例中,通过在开关节点与接地端之间增设电阻与电容,利用电阻消耗开关振铃产生的高频能量,从而实现振铃抑制效果。

但是,增设缓冲电路会产生额外损耗。若为提升抑制效果而增大电容容量,电阻需满足相应的功率耐受要求。以下是缓冲电路损耗的计算公式及示例。

缓冲电阻10Ω、焕荣电容1000pF、输入电压12V、振荡频率1MHz时的电阻允许损耗:

缓冲损耗 P = C × V2 × fSW

1000pF×122×1MHz=0.144W

*电阻额定功率需选用 MCR18(3216)系列:0.25W及以上规格

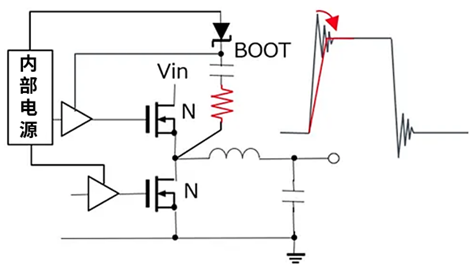

自举电路的噪声对策

开关噪声的另一个对策是“平缓开关波形的方法”。

采用Nch MOSFET作为高边开关的IC,大多配置有BOOT引脚。由于该引脚与开关节点相连,通过在引脚处插入电阻,可平缓高边MOSFET导通时的电压上升沿,进而抑制开关噪声。

总结:开关噪声对策与电路板布局的重要性

本页面详细阐述了开关噪声的相关细节,以及DC-DC转换器中开关噪声抑制对策的核心要点。其中关键原则是“尽量缩短布线长度”,这一措施对降低开关噪声具有显著作用。

若设计的电路及选定的元器件本身无问题,但实际使用中未能达到预期性能,甚至出现无法正常工作的极端情况,此时应优先检查电路板布局。此类问题在工程实践中并不少见,需特别注意。

为最大限度减少二次设计,提升包含电路板设计在内的整体设计质量至关重要。在布局设计中充分考量开关噪声的核心防控要点,是确保设计成功的关键所在。